# intel®

# 21145 Connection to the Network Using Physical Layer Devices

**Application Note**

July 1999

Order Number: 278293-001

# intel

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

The 21145 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1999

\*Third-party brands and names are the property of their respective owners.

# int<sub>el</sub>。 Contents

| 1.0 | Impler                   | nenting Network Connections1                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 1.1                      | Functional Overview21.1.121145 Overview21.1.2Network Interface21.1.3MII-Based PHY Block Diagram21.1.4SYM-Based PHY Block Diagram3                                                                                                                                                                                                                                                                                                                                       |

|     | 1.2<br>1.3               | 21145 Ports       4         Network Connection       5         1.3.1       10BASE-T Twisted-Pair Network Port.       5         1.3.2       100-Ready Designs       6         1.3.2.1       Internal Optional Daughtercard       7         1.3.2.2       Description of 100-Ready Daughtercard Block Diagram       7         1.3.2.3       100-Ready External Module Design       7         1.3.2.4       Description of 100-Ready External Module Block Diagram       8 |

|     |                          | 1.3.3       MII/SYM Pin Listing         1.3.4       Media-Specific Components                                                                                                                                                                                                                                                                                                                                                                                           |

|     | 1.4                      | 21145 Requirements       9         1.4.1       Current Reference and Capacitor Input Requirements         9       1.4.2         Crystal and Crystal Oscillator Connections         10                                                                                                                                                                                                                                                                                   |

|     | 1.5                      | Signal Routing and Placement111.5.1Ground and Power Planes111.5.1.13.3 V Power Supply12                                                                                                                                                                                                                                                                                                                                                                                 |

|     | 1.6                      | 1.5.2       LED Status Signals       12         Design Considerations       13         1.6.1       Designing the Ethernet Corner on Motherboards       13         1.6.2       Suggestions for FCC Compliance       14         1.6.2.1       Suggestions for Quiet Ground and Power Planes       14         1.6.2.2       Suggestions for Routing       14                                                                                                               |

| 2.0 | QS661                    | 11 SYM PHY Network Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | 2.1                      | QS6611 Overview       15         2.1.1       Features       15         2.1.1.1       Features and Benefits       16                                                                                                                                                                                                                                                                                                                                                     |

|     | 2.2<br>2.3               | QS6611 System Diagram.16QS6611 Schematic162.3.1 Network Connections162.3.2 21145 Connections182.3.3 Layout Considerations192.3.4 Ground-Plane Partitioning202.3.5 VCCPLL Connections21                                                                                                                                                                                                                                                                                  |

| 3.0 | DP838                    | 340A MII PHY Network Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 3.1<br>3.2<br>3.3<br>3.4 | DP83840A and DP83223V Overview.22DP83840A and DP83223V Block Diagram22DP83840A Description23DP83223V Description233.4.1Magnetics24                                                                                                                                                                                                                                                                                                                                      |

|     |            | 3.4.2     | DP83840A and DP83223V Schematic Diagram            | 24 |

|-----|------------|-----------|----------------------------------------------------|----|

|     |            | 3.4.3     | Media-Independent Interface (MII)                  | 24 |

|     |            | 3.4.4     | Signal Terminations                                | 25 |

|     |            |           | 3.4.4.1 Signal Transmission                        |    |

|     |            |           | 3.4.4.2 Signal Receive Operation                   | 27 |

|     |            | 3.4.5     | STP Operation                                      |    |

|     |            | 3.4.6     | Common-Mode Termination                            |    |

|     |            |           | 3.4.6.1 Transmit Active Pair Termination           |    |

|     |            |           | 3.4.6.2 Receive Active Pair Termination            |    |

|     |            |           | 3.4.6.3 Unused Pair Termination                    | 29 |

|     |            | 3.4.7     | Media Connections                                  |    |

|     | 3.5        | DP838     | 40A and DP83223V Layout Considerations             |    |

|     |            | 3.5.1     | Component Placement                                |    |

|     |            |           | 3.5.1.1 Special Considerations                     |    |

|     |            | 3.5.2     | General Guidelines                                 |    |

|     |            | 3.5.3     | Board Layers                                       |    |

|     |            | 3.5.4     | Ground Plane Partitioning                          |    |

|     | 3.6        |           | Requirements                                       |    |

|     | 0.0        | 3.6.1     | DP83840A and DP83223V Decoupling                   |    |

|     | 3.7        |           | 40A and DP83223V Parts List                        |    |

|     | 3.8        |           | 40A and DP83223V Summary                           |    |

|     |            |           | -                                                  |    |

| 4.0 | ICS18      | 890 MII P | HYceiver Network Implementation                    | 35 |

|     | 4.1        | ICS189    | 90 Overview                                        |    |

|     | 4.2        |           | 90 Block Diagram                                   |    |

|     | 4.3        |           | 90 Schematic Diagram Description                   |    |

|     | 1.0        | 4.3.1     | External Component Requirements                    |    |

|     |            | 4.3.2     | Schematic Information                              |    |

|     |            | 4.3.3     | External Component Listing                         |    |

|     |            | 4.3.4     | 10/100 Mb/s Magnetics Module Selection             |    |

|     |            | 4.3.4     | MII Data Interface                                 |    |

|     |            | 4.3.5     | 4.3.5.1 Carrier Sense and Collision Detect Signals |    |

|     |            | 126       | LED and PHY Pins                                   |    |

|     |            | 4.3.6     |                                                    |    |

|     |            | 4.3.7     | ICS1890 Power Supply and Layout Considerations     |    |

|     | 4 4        | 10040     | 4.3.7.1 Power Management Considerations            |    |

|     | 4.4        |           | 90 Summary                                         |    |

| 5.0 | NWK        | 914 SYM   | PHY Network Implementation                         |    |

|     | 5.1        | NWK9      | 14 Overview                                        | 48 |

|     | 5.2        |           | 14 Operation                                       |    |

|     | 0.2        | 5.2.1     | 10-Mb/s Transmit Operation                         |    |

|     |            | 5.2.2     | 100 Mb/s Transmit Operation                        |    |

|     |            | 5.2.2     | 10 Mb/s Receive Operation                          |    |

|     |            | 5.2.4     | 100-Mb/s Receive Operation                         |    |

|     | 5.3        |           | 14 Block Diagram                                   |    |

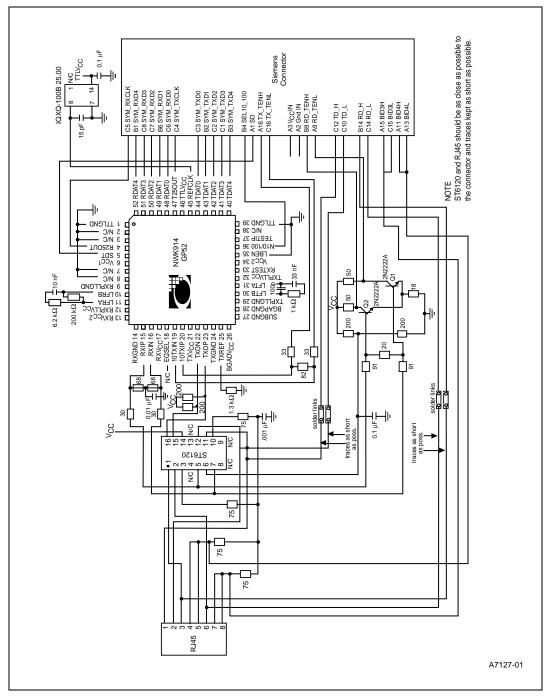

|     | 5.3<br>5.4 |           | the NWK914                                         |    |

|     | 0.4        | 5.4.1     | NWK914 Schematic                                   |    |

|     |            |           |                                                    |    |

|     |            | 5.4.2     | Layout Considerations                              |    |

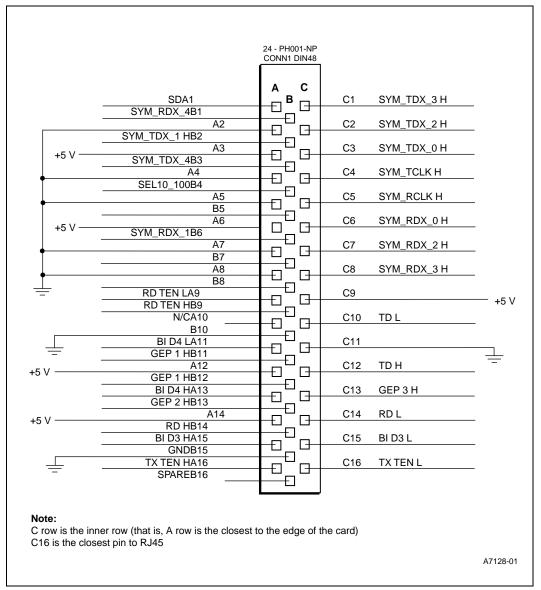

|     |            | 5.4.3     | 48-Pin DIN Connector                               |    |

|     |            | 5.4.4     | NWK914 Bill-of-Materials                           |    |

|     | 5.5        | Power     | Requirements                                       |    |

# intel®

|     | 5.6     | NWK914 Summary                                          | .59 |

|-----|---------|---------------------------------------------------------|-----|

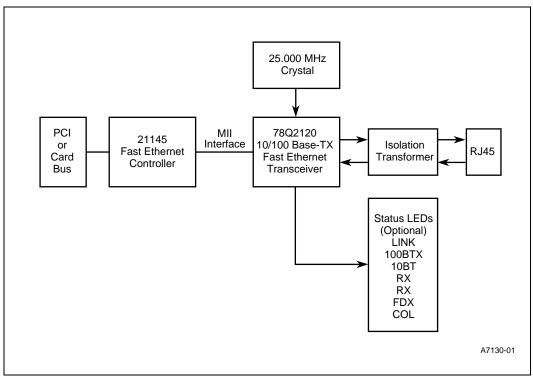

| 6.0 | TSC 78  | Q2120 MII PHY Network Implementation                    | .60 |

|     | 6.1     | 78Q2120 Overview                                        |     |

|     |         | 6.1.1 78Q2120 Features                                  |     |

|     | 6.2     | 78Q2120 Block Diagram                                   |     |

|     | 6.3     | 78Q2120 Description                                     | .62 |

|     |         | 6.3.1 Supply Voltage and Power Management               | .62 |

|     |         | 6.3.2 TX and RX Clock Selection                         |     |

|     |         | 6.3.3 100BASE-TX Transmit and Receive                   | .64 |

|     |         | 6.3.4 10BASE-T Transmit and Receive                     | .64 |

|     |         | 6.3.5 Auto-Negotiation                                  | .65 |

|     |         | 6.3.6 MII Interface                                     | .65 |

|     |         | 6.3.7 LED Indicators                                    | .66 |

|     |         | 6.3.8 General Purpose I/O Interface                     | .66 |

|     |         | 6.3.9 Interrupt Pin.                                    |     |

|     | 6.4     | 78Q2120 Schematic                                       |     |

|     |         | 6.4.1 78Q2120 Parts List                                | .67 |

|     | 6.5     | 10/100 Mb/s Transformer Selection                       |     |

|     | 6.6     | 78Q2120 Layout Considerations                           |     |

|     | 6.7     | 78Q2120 Summary                                         |     |

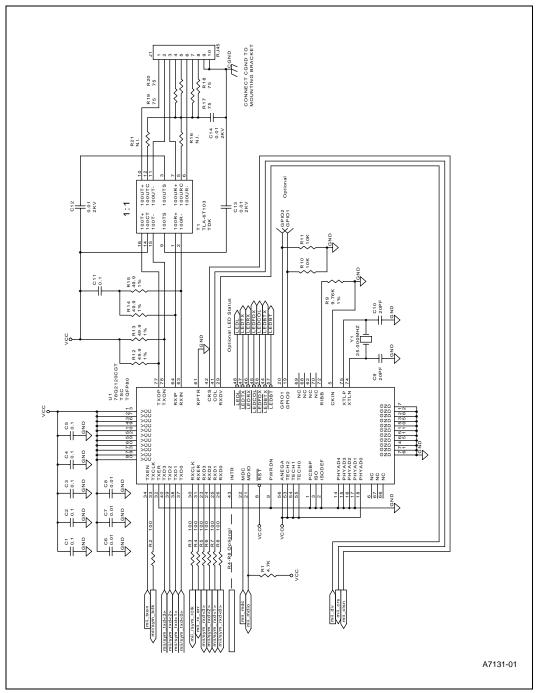

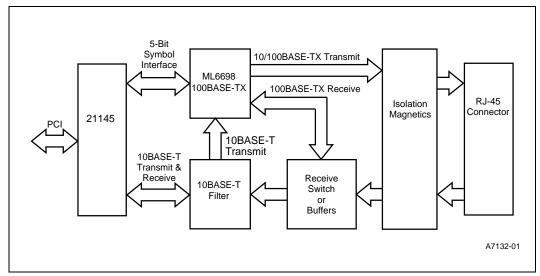

| 7.0 | ML6698  | 8 100 BASE-TX PHY                                       | .72 |

|     | 7.1     | ML6698 Overview                                         |     |

|     | 7.1     | Block Diagram                                           |     |

|     | 7.2     | Transmit and Receive Operation                          |     |

|     | 1.5     | •                                                       |     |

|     |         |                                                         |     |

|     |         | I                                                       |     |

|     |         | 7.3.3 10BASE-T Transmit Operation.                      |     |

|     |         | 7.3.4 Options for 10BASE-T Receive Operation            |     |

|     |         | 7.3.5 Wake-Up-LAN-Option Operation (Demonstration Only) |     |

|     | 7 4     | 7.3.6 Other Considerations                              |     |

|     | 7.4     | Layout Considerations                                   |     |

|     | 7.5     | ML6698 Summary                                          |     |

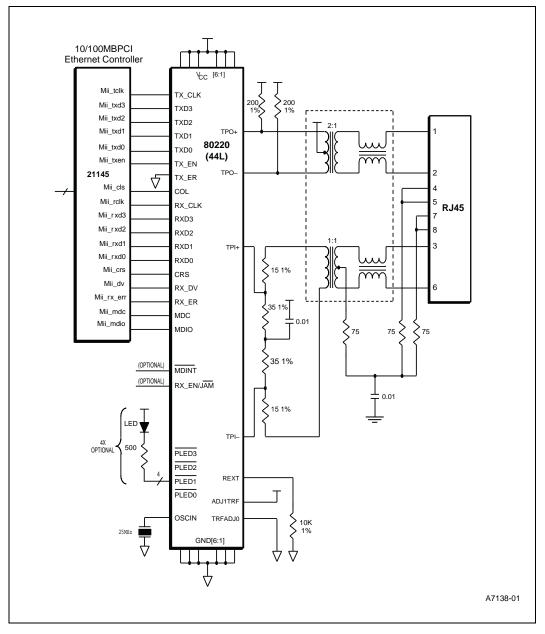

| 8.0 | 80220/8 | 80221 10/100BASE-TX PHY                                 | .85 |

|     | 8.1     | Overview                                                | .85 |

|     | 8.2     | Interface to the 21145                                  | .85 |

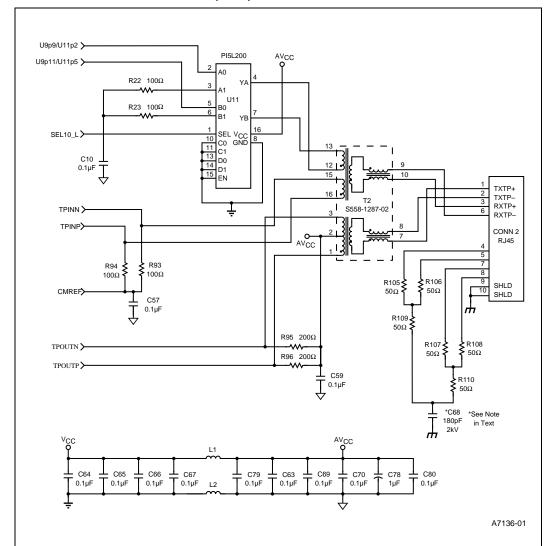

|     | 8.3     | 80220 PHY Board Schematic Diagram                       | .87 |

|     | 8.4     | Design Considerations                                   | .88 |

|     |         | 8.4.1 Choosing a Transformer                            | .88 |

|     |         | 8.4.2 Termination Requirements                          | .89 |

|     |         | 8.4.3 Meeting IEEE-Specified Output Amplitude Levels    | .90 |

|     |         | 8.4.4 MII Interface                                     |     |

|     |         | 8.4.5 Clock Requirements                                | .90 |

|     | 8.5     | Programming Considerations                              |     |

|     |         | 8.5.1 Determination of the PHY Address                  |     |

|     |         | 8.5.2 Initialization                                    |     |

|     |         | 8.5.3 Configurations                                    |     |

|     | 8.6     | Layout Guidelines                                       |     |

|     |         | 8.6.1 Decoupling                                        |     |

|     |         |                                                         |     |

9.0

# int<sub>el</sub>.

|            | 8.6.2<br>8.6.3 | Traces<br>Power Planes                                | 93  |

|------------|----------------|-------------------------------------------------------|-----|

| ~ <b>-</b> | 8.6.4          | Clock Considerations                                  |     |

| 8.7        | 80220/8        | 30221 Summary                                         | 93  |

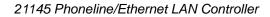

| LXT97      | ) Fast Et      | hernet Transceiver                                    | 94  |

| 9.1        | LXT970         | ) Overview                                            | 94  |

| 9.2        | Block D        | liagram                                               | 94  |

| 9.3        | MII Inte       | rface                                                 | 95  |

|            | 9.3.1          | MII Data Interface                                    | 95  |

|            |                | 9.3.1.1 4-Bit Nibble Mode and 5-Bit Symbol Mode       | 95  |

|            | 9.3.2          | MII Connection                                        | 95  |

|            | 9.3.3          | MII Management Interface                              | 96  |

|            | 9.3.4          | MII Registers                                         | 96  |

| 9.4        | Hardwa         | re Control Interface                                  | 97  |

|            | 9.4.1          | Multifunction Pins                                    | 97  |

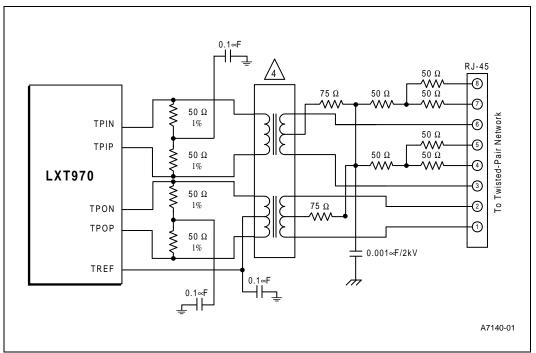

| 9.5        | Network        | k Connection                                          | 99  |

|            | 9.5.1          | Magnetics                                             | 99  |

|            | 9.5.2          | Schematic Information                                 | 101 |

| 9.6        | Externa        | I Components                                          | 102 |

|            | 9.6.1          | Clock Requirements                                    | 102 |

| 9.7        | Layout         | Requirements                                          |     |

|            | 9.7.1          | Twisted-Pair Interface Layout Considerations          | 103 |

|            | 9.7.2          | Plane Layout Considerations                           | 103 |

|            | 9.7.3          | The RBIAS Pin                                         | 103 |

|            | 9.7.4          | Power Supply Decoupling                               | 104 |

|            | 9.7.5          | Bypass Caps                                           | 104 |

|            | 9.7.6          | MII Interface                                         | 104 |

|            | 9.7.7          | Voltage Divider for MF Inputs                         | 104 |

| 9.8        | LXT970         | ) Summary                                             | 105 |

| Nationa    | al Semico      | onductor License Agreement                            | 106 |

| A.1        | Commo          | on Magnetics License Agreement                        | 106 |

| A.2        |                | I Semiconductor Physical Layer Design Recommendations |     |

# Figures

А

| 1  | MII-Based PHY Design                             | 3  |

|----|--------------------------------------------------|----|

| 2  | SYM-Based PHY Design                             |    |

| 3  | Minimum Components Required for 10BASE-T         | 6  |

| 4  | 10BASE-T 100-Ready Daughtercard Block Diagram    |    |

| 5  | 10BASE-T 100-Ready External Module Block Diagram | 8  |

| 6  | 21145 External Component Connections             | 10 |

| 7  | LED Time-Stretcher Circuit                       | 13 |

| 8  | QS6611 System Diagram                            | 16 |

| 9  | QS6611 Connection to the RJ45-8                  | 17 |

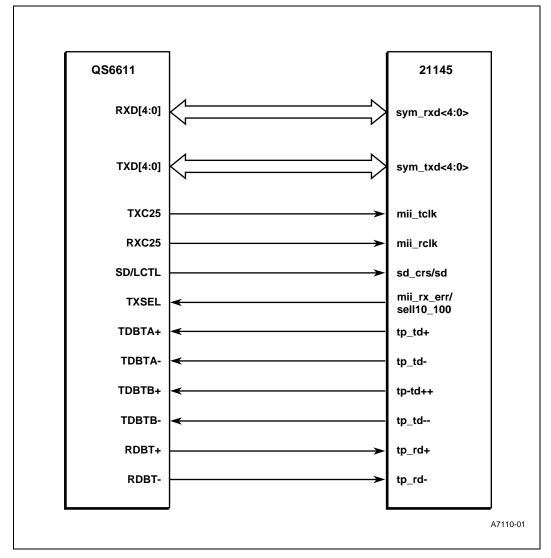

| 10 | Connecting the QS6611 to the 21145               |    |

| 11 | PWB Noise Reduction                              | 20 |

# intel®

| 40 |                                                          | 04  |

|----|----------------------------------------------------------|-----|

| 12 | Connecting the VCCPLL on the QS6611                      |     |

| 13 | 10/100 Mb/s Block Diagram                                |     |

| 14 | Microstrip impedance                                     |     |

| 15 | Physical Layer Component Placement Recommendation        |     |

| 16 | Board Layer Recommendation                               |     |

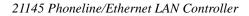

| 17 | ICS1890 Block Diagram                                    |     |

| 18 | ICS1890 Schematic Diagram                                |     |

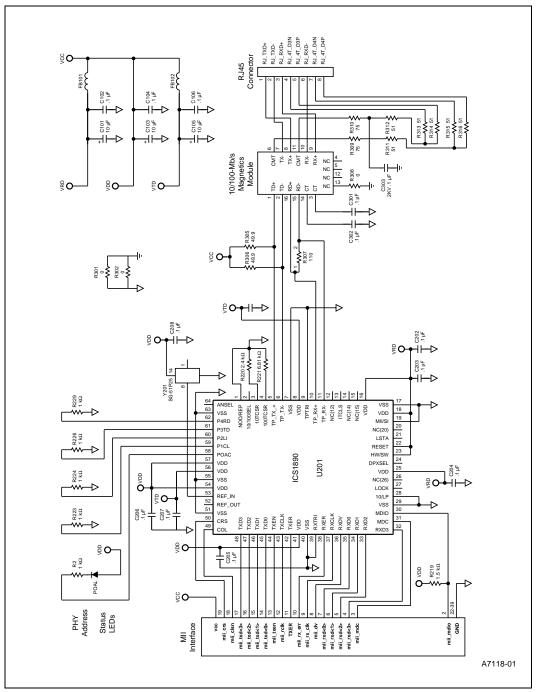

| 19 | 10/100 Mb/s Magnetics Module Data Paths                  |     |

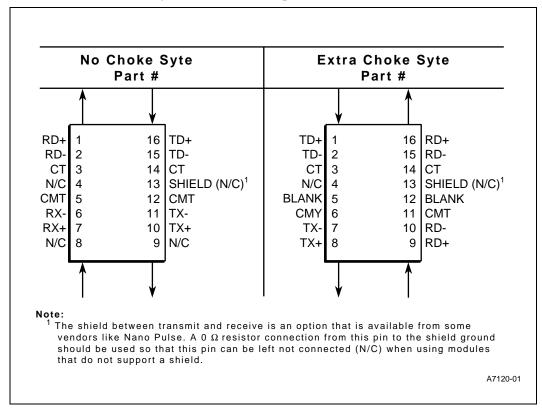

| 20 | No Choke, Extra Choke Style Transformer Footprints       |     |

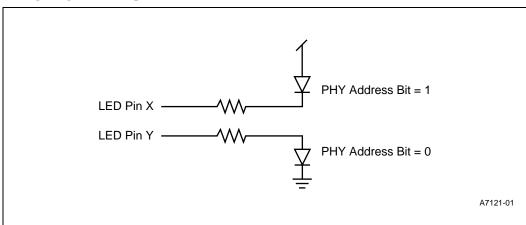

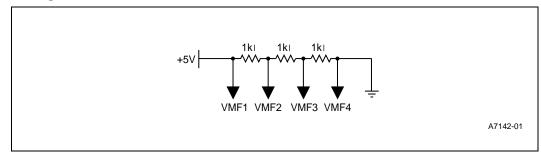

| 21 | Configuring LED Components                               |     |

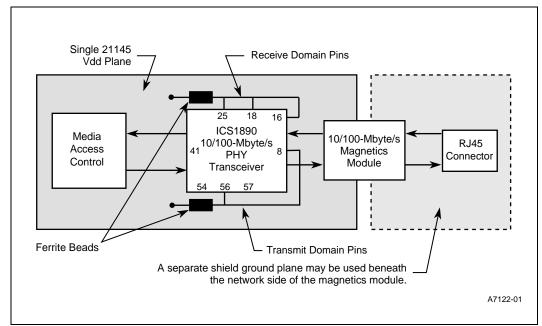

| 22 | Single Vdd Plane Isolation                               |     |

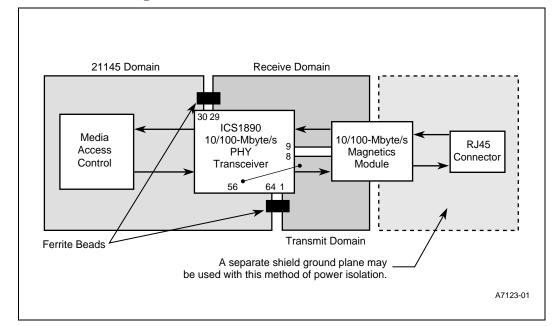

| 23 | ICS1890 Power Management Considerations                  |     |

| 24 | Transmit Operation                                       |     |

| 25 | Receive Operation                                        |     |

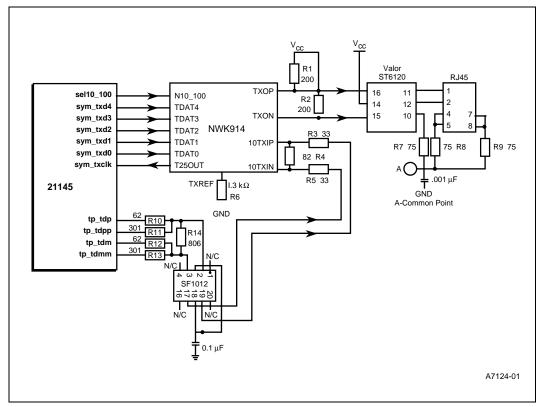

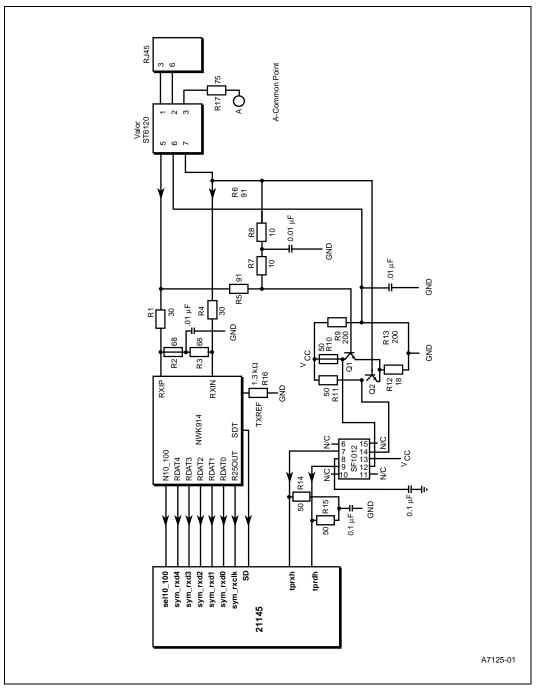

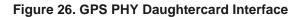

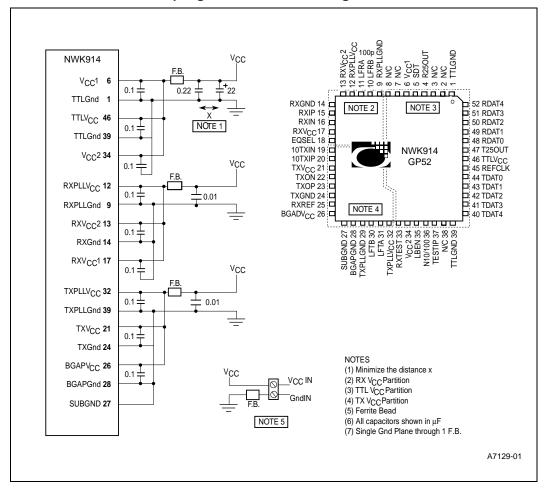

| 26 | GPS PHY Daughtercard Interface                           |     |

| 27 | GPS PHY Daughtercard Schematic                           |     |

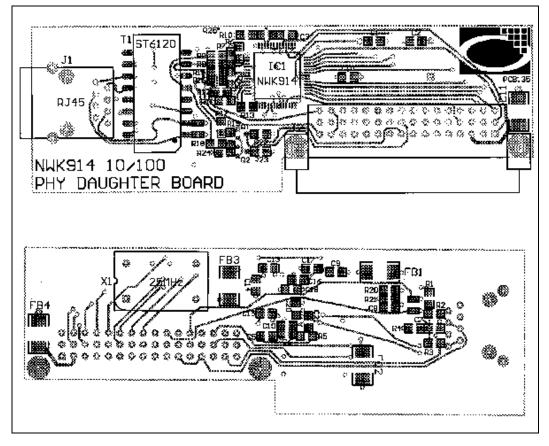

| 28 | NWK914 10/100 PHY Daughtercard Layout                    |     |

| 29 | 48-Pin DIN Connector                                     |     |

| 30 | Power Planes and Decoupling for the GPS PHY Daughtercard |     |

| 31 | 78Q2120 Block Diagram                                    |     |

| 32 | 78Q2120 Schematic Diagram                                |     |

| 33 | PCI Adapter Block Diagram: Signal Flow                   |     |

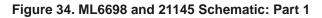

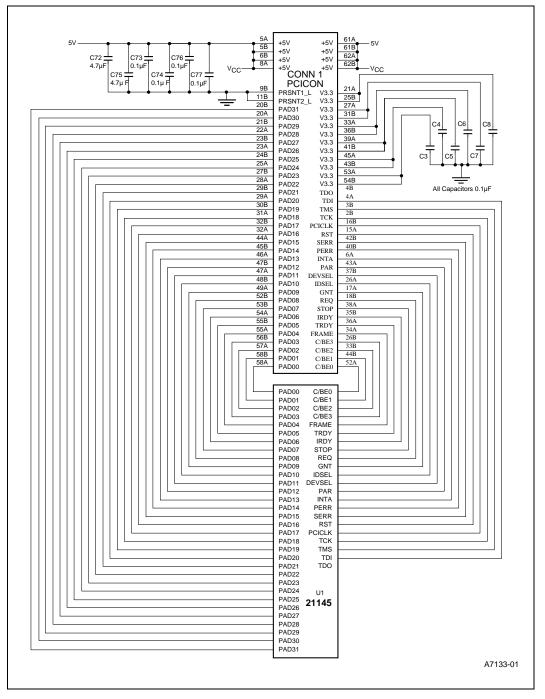

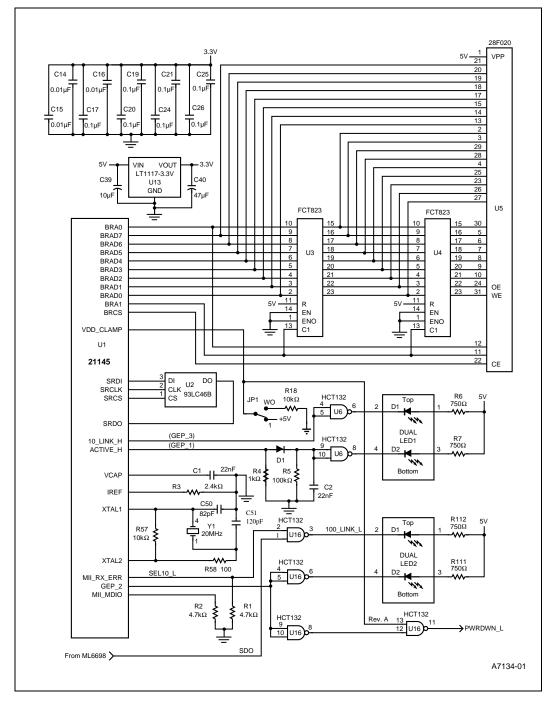

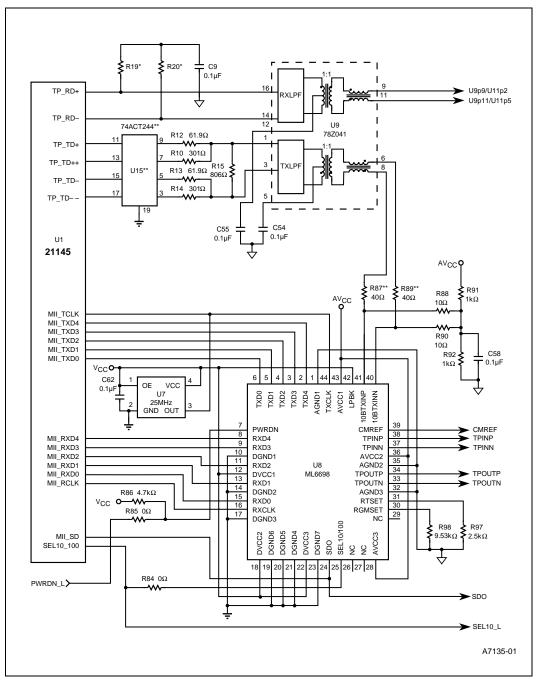

| 34 | ML6698 and 21145 Schematic: Part 1                       |     |

| 35 | ML6698 and 21145 Schematic: Part 2                       |     |

| 36 | ML6698 and 21145 Schematic: Part 3                       |     |

| 37 | ML6698 and 21145 Schematic: (MUX)                        |     |

| 38 | ML6698 and 21145 Schematic: (Buffer)                     |     |

| 39 | 80220 PHY Board Block Diagram                            |     |

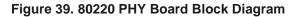

| 40 | Network Connection                                       |     |

| 41 | Twisted-pair Interface                                   |     |

| 42 | LXT970 Schematic                                         |     |

| 43 | Voltage Divider                                          |     |

| 44 | 10/100 Ethernet Physical Layer Block Diagram             |     |

| 45 | DP83840A                                                 |     |

| 46 | DP83223V                                                 |     |

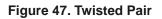

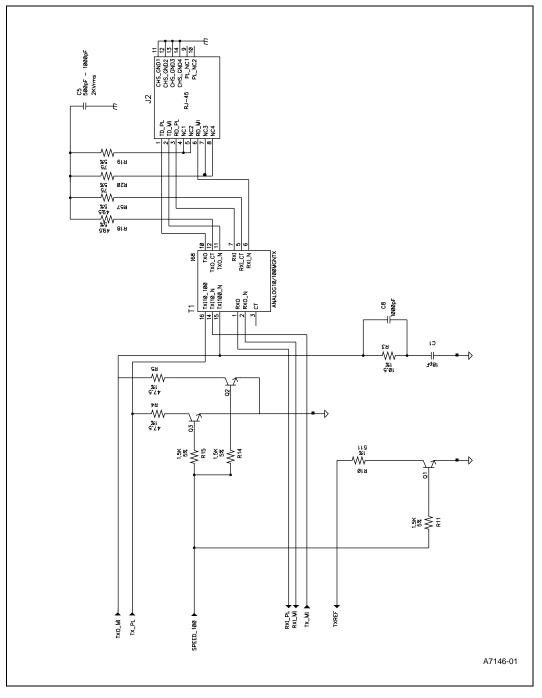

| 47 | Twisted Pair                                             |     |

| 48 | MII Interface                                            | 111 |

# Tables

| 1 | Twisted-Pair Signals                   | 4  |

|---|----------------------------------------|----|

| 2 | MII Signals                            |    |

| 3 | SYM Signals                            |    |

| 4 | Internal vs. External Design Features  |    |

| 5 | MII/SYM Pinout                         |    |

| 6 | 10BASE-T Media-Specific Components     | 9  |

| 7 | Current Reference and Capacitor Inputs | 10 |

| 8 | Crystal Specifications                 | 11 |

| 9 | QS6611 Features and Benefits           | 16 |

# intel®

| 10 | QS6611 PWB Layout Recommendations                       | 19 |

|----|---------------------------------------------------------|----|

| 11 | Component Values Required for STP or UTP Operation      | 28 |

| 12 | Unshielded Twisted-Pair RJ45-8 Connector                | 29 |

| 13 | Shielded Twisted-Pair DB-9 Connector                    |    |

| 14 | Recommended Parts List for DP83840A and DP83223V        | 33 |

| 15 | ICS1890 External Components                             |    |

| 16 | 10/100 Mb/s Magnetic Module Vendors                     | 39 |

| 17 | 21145 to ICS1890 Interface Signal Mapping               | 42 |

| 18 | MII Carrier Sense and Collision Detect Signal Operation |    |

| 19 | Methods for Filtering Noise                             | 44 |

| 20 | Power Supply Filtering                                  |    |

| 21 | ICS1890 Power Consumption                               |    |

| 22 | NWK914 Bill-of-Materials                                |    |

| 23 | TSC 78Q2120 Recommended Operating Conditions            | 62 |

| 24 | 78Q2120 Power Consumption                               |    |

| 25 | 78Q2120 Parts List                                      |    |

| 26 | Line Transformer Characteristics                        |    |

| 27 | Acceptable Transformers                                 |    |

| 28 | 21145 and ML6698 Board Parts List                       |    |

| 29 | 80220 PHY Board Component Listing                       |    |

| 30 | Transformer Parameters                                  |    |

| 31 | Transformer Vendors                                     |    |

| 32 | Termination Specifications                              |    |

| 33 | Crystal Specifications                                  | 90 |

| 34 | Vcc-Gnd Pair                                            |    |

| 35 | 21145 MII Connection                                    |    |

| 36 | 21145 SYM Connection                                    |    |

| 37 | MII Registers                                           |    |

| 38 | MF Pin Functions                                        |    |

| 39 | Operating Advertisement Capabilities                    |    |

| 40 | Suitable Magnetics                                      |    |

| 41 | Suitable Crystals1                                      |    |

| 42 | 21145/LXT970 NIC External Components1                   | 02 |

# **1.0** Implementing Network Connections

This application note provides a description of how to implement 100BASE-TX and 10BASE-T network connections using the 21145 Phoneline/Ethernet LAN Controller (referred to as the 21145).

While this document will not provide specific recommendations for physical layer devices, it will provide design recommendations and layout recommendations using media-independent interface (MII) based physical layer devices provided by, Integrated Circuit Systems, National Semiconductor, Level One, and Seeq, and symbol (SYM) based physical layer devices provided by Mitel, Quality Semiconductor, and Micro Linear. Throughout this document, a physical layer device is referred to as a PHY or PHY device.

The devices covered in this application note are the following:

- QS6611 SYM PHY

- DP83840A MII PHY

- ICS1890 MII PHY

- TSC 78Q2120 MII PHY

- ML6698 100BASE-TX PHY

- 80220/80221 10/100BASE-TX PHY

- LXT970 Fast Ethernet Transceiver.

This application note was developed with the cooperation and input from different PHY manufacturers. In some cases, these manufacturers or Intel may have sample boards available to aid in your evaluation. Please check with the PHY manufacturer for the latest information available for each specific device.

*Note:* This application note does not describe the 21145 software interface. For more information on the software interface, refer to the 21145 Phoneline/Ethernet LAN Controller Hardware Reference Manual.

# **1.1 Functional Overview**

This section provides an overview of the 21145 and the implementation of 100 Mb/s and 10 Mb/s network connections using MII-based or SYM-based PHY devices.

#### 1.1.1 21145 Overview

The 21145 is a single-chip bus master Ethernet/Fast Ethernet device that supports direct memory access (DMA) and has direct interfaces to both the CardBus and the PCI local bus. The 21145 implements a direct interface to the CardBus or PCI bus, which consists of the control and address/data signals.

The 21145 provides a complete implementation of the IEEE 802.3 Ethernet specification. This includes the twisted-pair (10BASE-T) interface, MII SYM port interface, and the interface through the media access control (MAC) layer that creates a direct interface to the PCI bus.

The PCI interface utilizes only about 10% of the bus bandwidth during fully networked operation for 100 Mb/s Fast Ethernet reception or transmission. This bus master design results in high throughput between the system and the network.

#### **1.1.2** Network Interface

The 21145 physical layer design supports 10BASE-T twisted-pair (TP) Ethernet connections. The 21145 implements the 100BASE-T MII layer and the 100/10 Mb/s Ethernet MAC layer. The 21145 provides a dual network interface for both a 100BASE-T and a 10 Mb/s Ethernet. At the 100BASE-T port, the 21145 supports the industry-standard MII for any 100BASE-T implementation.

The 21145 is fully compliant with the MII specifications (as defined in IEEE 802.3). The MII is a nibblewide, general interface, that can be used with various physical interfaces, such as 100BASE-TX, 100BASE-T4, shielded twisted-pair (STP), and fiber. It also supports dual rates of speed (10 Mb/s and 100 Mb/s).

The 21145 includes special support for 100BASE-TX networks by including the PCS section (scrambler and 5B/4B coding/decoding). Integrating the 10BASE-T ENDEC with the 100 Mb/s-only SYM-based PHYs enables full support for a 10/100-implementation.

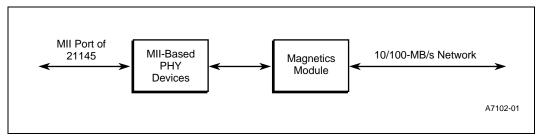

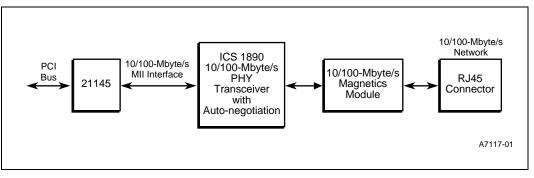

### 1.1.3 MII-Based PHY Block Diagram

Figure 1 is a block diagram of a 10BASE-T and 100BASE-T single-connector network connection using a MII-based PHY device with the 21145.

MII-based PHY devices are provided by Integrated Circuit Systems, National Semiconductor, Level One, Seeq, and TDK.

Figure 1. MII-Based PHY Design

The MII-based PHY design includes the following components:

- The MII-based PHY devices, which have a direct interface to the MII port of the 21145 with dual-rate option (as specified in the MII specification) and a full interface to the 10/100 Mb/s magnetics module.

- The magnetics module, which is based on transformers and serial chokes enabling the network connection to the 100 Mb/s network (100BASE-TX or 100BASE-T4) and to the 10 Mb/s network (10BASE-T).

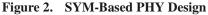

### 1.1.4 SYM-Based PHY Block Diagram

Figure 2 is a block diagram of a 100BASE-TX single-connector network connection using a SYM-based PHY device with the 21145. For a 10 Mb/s network connection, the network can be connected directly to the 21145 through filters and chokes.

SYM-based PHY devices are provided by Mitel, Quality Semiconductor, and Micro Linear.

The SYM-based PHY design includes the following components:

- The SYM-based PHY devices, which have a direct interface to the SYM port of the 21145 with an interface to the 100 Mb/s magnetics module.

- The magnetics module, which is based on transformers and serial chokes enabling the network connection to the 100 Mb/s-only network (100BASE-TX or 100BASE-T4).

# 1.2 21145 Ports

Table 1 lists the active twisted-pair signals when the 21145 10BASE-T port is selected.

#### Table 1.Twisted-Pair Signals

| Signal   | 144-Pin Package Pin Number | 176-Pin Package Pin Number |

|----------|----------------------------|----------------------------|

| tp_rd-   | 10                         | 10                         |

| tp_rd+   | 9                          | 9                          |

| tp_td-   | 5                          | 5                          |

| tp_td    | 4                          | 4                          |

| tp_td+   | 6                          | 6                          |

| tp_td+ + | 7                          | 7                          |

Table 2 lists the active MII signals when the 21145 MII port is selected.

#### Table 2. MII Signals

| Signal        | 144-Pin Package Pin Number | 176-Pin Package Pin Number |

|---------------|----------------------------|----------------------------|

| mii_clsn      | 118                        | 147                        |

| mii_crs       | 117                        | 146                        |

| mii_dv        | 129                        | 161                        |

| mii_mdc       | 134                        | 166                        |

| mii_mdio      | 135                        | 167                        |

| mii_rclk      | 128                        | 160                        |

| mii_rx_err    | 127                        | 159                        |

| mii_rxd <3:0> | 133:130                    | 165:162                    |

| mii_tclk      | 124                        | 153                        |

| mii_txd<3:0>  | 119:122                    | 151:148                    |

| mii_txen      | 123                        | 152                        |

Table 3 lists the active SYM signals when the 21145 SYM port is selected.

#### Table 3.SYM Signals (Sheet 1 of 2)

| Signal     | 144-Pin Package Pin Number | 176-Pin Package Pin Number |

|------------|----------------------------|----------------------------|

| sd         | 117                        | 146                        |

| sel10_100  | 127                        | 159                        |

| sym_rclk   | 128                        | 160                        |

| sym_rxd<0> | 130                        | 162                        |

| sym_rxd<1> | 131                        | 163                        |

| sym_rxd<2> | 132                        | 164                        |

| sym_rxd<3> | 133                        | 165                        |

| sym_rxd<4> | 118                        | 147                        |

| sym_tclk   | 124                        | 153                        |

| sym_txd<0> | 122                        | 151                        |

#### Table 3.SYM Signals (Sheet 2 of 2)

| Signal     | 144-Pin Package Pin Number | 176-Pin Package Pin Number |

|------------|----------------------------|----------------------------|

| sym_txd<1> | 121                        | 150                        |

| sym_txd<2> | 120                        | 149                        |

| sym_txd<3> | 119                        | 148                        |

| sym_txd<4> | 123                        | 152                        |

# **1.3** Network Connection

The network connections of the 21145 can be used in 10BASE-T, MII, or SYM configurations. Different methods are used to connect each port to the actual cable connector.

#### **1.3.1 10BASE-T Twisted-Pair Network Port**

Figure 3 shows the network connection design options for 10BASE-T type implementations. Figure 3 shows a direct connection to a  $1:\sqrt{2}$  transformer module. This implementation type provides the lowest component count for 10BASE-T. The filter and transformer components minimize any potential electromagnetic interference and radio frequency interface problems. Common-mode noise (when noise between two lines of the same polarity *add* rather than cancel) can radiate energy from the twisted-pair interface. Also, significant common-mode power supply noise can be generated on the board or adapter by other devices. Therefore, Intel recommends the use of filter and transformer modules that incorporate common-mode chokes.

Figure 3 shows the minimum component requirement for the 10BASE-T network connection. This implementation uses a filter transformer module with a  $1:\sqrt{2}$  transformer on the transmit path to compensate for the voltage swing. The required components for this configuration are as follows:

- Terminating and decoupling components

- Filter, transformer, and common-mode chokes

- RJ45 connector

# intel

Figure 3. Minimum Components Required for 10BASE-T

#### 1.3.2 100-Ready Designs

The 21145 can also be designed for systems that are "100-Ready." The term "100-Ready" implies a system that has a 10 Mb/s network that can easily be upgraded to become a 10/100 Mb/s network. There are two methods for providing 100-Ready designs:

- Provide a connector for an internal optional daughtercard.

- Provide an MII connector for an external module that connects to the MII/SYM port.

These two methods are described in Table 4.

Table 4.

Internal vs. External Design Features

| Design                         | Features                                                                                                                            |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Internal optional daughtercard | <ul><li>Can be designed with an MII or any custom connector.</li><li>User opens cabinet to install 100 Mb/s daughtercard.</li></ul> |

| External MII/SYM module        | • User connects module to external MII/SYM connector; user does not have to open cabinet for installation.                          |

### **1.3.2.1** Internal Optional Daughtercard

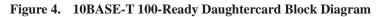

Figure 4 shows a block diagram of a 100-Ready design using a daughter card.

### 1.3.2.2 Description of 100-Ready Daughtercard Block Diagram

The blocks in the10BASE-T 100-Ready block diagram represent the following components:

- 21145 A 21145 with all of the external components for operating the network connection (reference parts, XTAL, and so on). The 21145 can use the PCI bus and the MII/SYM, 10BASE-T ports for communication.

- Optional MII/SYM daughtercard A daughtercard with a 100 Mb/s or 10/100 Mb/s PHY that interfaces with an MII connector or custom connector. The daughtercard can be designed to use the same RJ45 connector.

- RJ45 A network connection.

### 1.3.2.3 100-Ready External Module Design

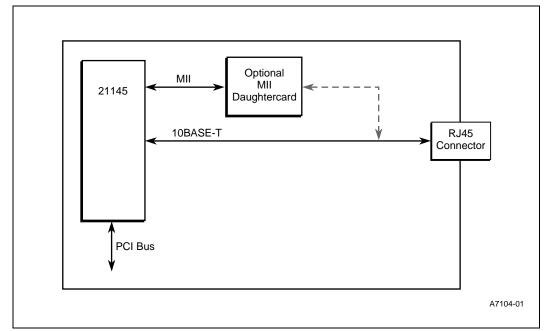

Figure 5 shows a block diagram of a 100-Ready design using an external module.

Figure 5. 10BASE-T 100-Ready External Module Block Diagram

### 1.3.2.4 Description of 100-Ready External Module Block Diagram

The blocks in the 100-Ready external module block diagram represent the following components:

- 21145—A 21145 with all of the external components for operating the network connection (reference parts, XTAL, and so on). The 21145 can use the PCI bus, and the MII/SYM, 10BASE-T ports for communication.

- Optional external MII/SYM daughtercard—A daughtercard with a 100 Mb/s or 10/100 Mb/s PHY that interfaces with an MII connector or custom connector. The daughtercard uses the magnetics to connect to the RJ45 connector.

- MII connector—An MII or custom connector that connects with the MII/SYM port of the 21145.

- RJ45—A network connection.

#### 1.3.3 MII/SYM Pin Listing

Table 5 describes the MII/SYM pin multiplexing enabling the full flexibility for both network connections options using the same internal connector for the MII-based or the SYM-based PHY device (for detailed implementation notes, refer to the specific PHY device section in this document).

Table 5.MII/SYM Pinout (Sheet 1 of 2)

| 144-Pin Package Pin<br>Number | 176-Pin Package Pin<br>Number | MII Interface Function | SYM Interface Function |

|-------------------------------|-------------------------------|------------------------|------------------------|

| 117                           | 146                           | mii_crs                | sd                     |

| 118                           | 147                           | mii_clsn               | sym_rxd<4>             |

| 119                           | 148                           | mi_txd<3>              | sym_txd<3>             |

| 144-Pin Package Pin<br>Number | 176-Pin Package Pin<br>Number | MII Interface Function | SYM Interface Function |  |  |

|-------------------------------|-------------------------------|------------------------|------------------------|--|--|

| 120                           | 149                           | mi_txd<2>              | sym_txd<2>             |  |  |

| 121                           | 150                           | mi_txd<1>              | sym_txd<1>             |  |  |

| 122                           | 151                           | mii_txd<0>             | sym_txd<0>             |  |  |

| 123                           | 152                           | mii_txen               | sym_txd<4>             |  |  |

| 124                           | 153                           | mii_tclk               | sym_tclk               |  |  |

| 127                           | 159                           | mii_rx_err             | sel10_100              |  |  |

| 128                           | 160                           | mii_rclk               | mii_rclk               |  |  |

| 129                           | 161                           | mii_dv                 | N.C.                   |  |  |

| 130                           | 162                           | mii_rxd<0>             | sym_rxd<0>             |  |  |

| 131                           | 163                           | mii_rxd<1>             | sym_rxd<1>             |  |  |

| 132                           | 164                           | mii_rxd<2>             | sym_rxd<2>             |  |  |

| 133                           | 165                           | mii_rxd<3>             | sym_rxd<3>             |  |  |

| 134                           | 166                           | mii_mdc                | N.C.                   |  |  |

| 135                           | 167                           | mii_mdio               | N.C.                   |  |  |

Table 5.MII/SYM Pinout (Sheet 2 of 2)

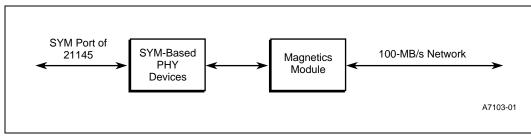

### **1.3.4** Media-Specific Components

Table 6 lists the media-specific interface components for 10BASE-T access.

Table 6.

10BASE-T Media-Specific Components

| Access Type | Components                     | Available Part Numbers  |

|-------------|--------------------------------|-------------------------|

| 10BASE-T    | Filter, transformer and chokes | Pulse Engineering E2009 |

| _           | RJ45 wire jack connector       | —                       |

# 1.4 21145 Requirements

This section provides information about the external component connections for the 21145, and describes the following requirements:

- Current reference and capacitor input

- Crystal connection or crystal oscillator connection for the serial clock connection

### 1.4.1 Current Reference and Capacitor Input Requirements

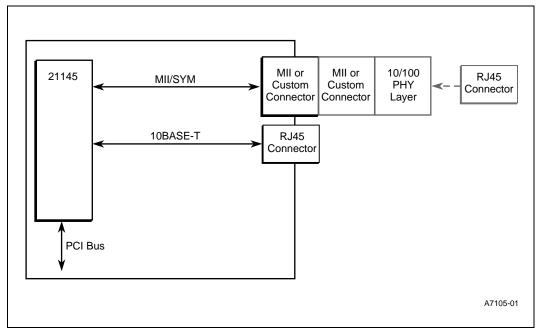

Table 7 describes the current reference and capacitor input requirements for the 21145, and Figure 6 shows the external component connections.

# intel

| Table 7.         Current Reference and Capacitor Inputs |

|---------------------------------------------------------|

|---------------------------------------------------------|

| Pin Name | 144-Pin<br>Package Pin<br>Number | 176-Pin<br>Package Pin<br>Number | Function                                                       | Connect This Pin                             |

|----------|----------------------------------|----------------------------------|----------------------------------------------------------------|----------------------------------------------|

| iref     | 108                              | 132                              | Current reference input for the analog phase-locked loop (PLL) | Through a 2.43 k $\Omega$ resistor to ground |

| vcap_h   | 110                              | 134                              | Capacitor input                                                | Through a 0.022 $\mu$ F capacitor to ground  |

Figure 6. 21145 External Component Connections

# 1.4.2 Crystal and Crystal Oscillator Connections

Figure 6 shows two serial clock connections; select either the crystal connection or the crystal oscillator connection. According to the IEEE 802.3 standard, a 20 MHz crystal is required. The crystal frequency must not vary by more than 100 parts per million (PPM), or 0.01%. Place the crystal as close as possible to the 21145.

Because the frequency of crystals from different vendors can vary, test the crystals in the actual circuit. It may be necessary to vary the tuning of the surrounding components. However, after the capacitors have been tuned for the specific crystal, the design does not need to be altered on a board-by-board basis.

The 21145 also supports a crystal oscillator (Figure 6). This configuration requires no external component and xtal2 should be left open. This is useful for applications with multiple network connections.

Table 8 lists the crystal specifications.

#### Table 8. Crystal Specifications

| Specification                       | Value  | Units    |  |  |

|-------------------------------------|--------|----------|--|--|

| Crystal frequency                   | 20.000 | MHz      |  |  |

| Frequency tolerance                 | ±50    | PPM      |  |  |

| Load capacitance                    | 50     | pF       |  |  |

| Frequency stability                 | ±30    | PPM      |  |  |

| Maximum effective series resistance | 40     | Ohms (Ω) |  |  |

| Test condition drive level          | 100    | μW       |  |  |

# **1.5** Signal Routing and Placement

The Ethernet circuitry should be kept free of interference from unrelated signal traces. Routing for other signals must be kept away from the space surrounding the grouped Ethernet components. Place the Ethernet circuitry at the perimeter of the board, as close as possible to the network connector.

The onchip crystal oscillator requires an external crystal and discrete components. For stable and noise-free operation, place the crystal and discrete components as close as possible to the 21145, keeping the etch length as short as possible. Do not route any noisy signals in this area.

The PCI pin ordering is fully compatible with the PCI specification recommendation and can be easily routed within the specified etch limits of the PCI signals. This includes shared signal lengths of up to 3.8 cm (1.5 in) and the clock signal length of 6.41 cm (2.5 in).

Keep all signal paths short and route them as directly as possible.

Systems using 10BASE-T nodes can be connected by cables up to 100 m (328 ft.). As a result, signals that reach the board can be noisy and low in amplitude. To minimize corrupting this data, route these signals, by most direct path, from the network connector and through the magnetics coupler to the 21145.

The length of this path should not exceed 8 cm (3 in) for the active signals. The MII/SYM interface operates at 25 MHz (or 2.5 MHz). All routing of the MII/SYM signals to the MII/SYM device should be as short as possible and should not have significant differences of lengths and characteristics within signal groups. Examples of signal groups include mii\_rxd<4:0> and mii\_txd<4:0>.

*Note:* The routing of these signals should be done with caution. The preferred routing of these signals is in the external routing layers of the board. The MII/SYM device should be located between the 21145 and the magnetics port.

### 1.5.1 Ground and Power Planes

Up to four types of power signals require handling when implementing a design with the 21145:

- Gnd is adapter ground.

- Vcc (+5 V from PCI) drives the external components (boot ROM and Ethernet address ROM).

- Vdd (+3.3 V) drives the 21145.

Intel recommends that at least two power planes be kept on the PCB: Vcc and Gnd. The Vdd power plane (+3.3 V) can be implemented either by a cut in the Vcc power plane, or by a power island under the 21145 on one of the signal routing layers.

# intel®

Intel recommends that decoupling capacitors should be connected to all power supplies. These capacitors should be placed as close as possible to the power pins of the chips. The recommended values are as follows: 0.1  $\mu$ F, 0.01  $\mu$ F, 10  $\mu$ F (tantalum), and 47  $\mu$ F (tantalum).

For better noise-testing immunity, separate all power planes between the network connectors and the transformer from the logic and analog power planes of the adapter for the 10BASE-T, and 100BASE-TX connections.

Intel also recommends that the connector's shield of the adapter should be connected to the PC chassis.

# 1.5.1.1 **3.3 V Power Supply**

The 21145 operates with a power supply of 3.3 V. At least eight decoupling capacitors are recommended and should contain the following values:

- Three each at 0.1 µF

- Three each at 0.01 µF

- One each at 10 µF (tantalum)

- One each at 47 µF (tantalum)

#### **1.5.2 LED Status Signals**

The LED connection requires a serial resistor that is connected to ground. This resistor value should be calculated according to the type of LED used. A typical 2 mA LED requires a 750  $\Omega$  resistor. For implementations using the boot ROM, the LED current should not exceed 2 mA. For LED indication and programming information, refer to the CSR15 definition in the 21145 Phoneline/Ethernet LAN Controller Hardware Reference Manual.

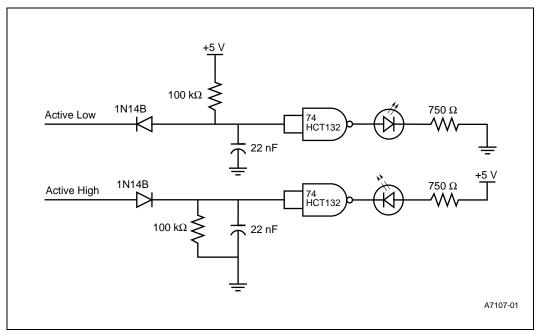

The 21145 requires LED time-stretching logic for a visible indication of the activity signal. Figure 7 shows how to implement this circuit.

Figure 7. LED Time-Stretcher Circuit

# **1.6 Design Considerations**

This section provides information to aid the user in designing Ethernet and Fast Ethernet capabilities onto a motherboard. In addition, it also includes design considerations for FCC compliance.

#### **1.6.1** Designing the Ethernet Corner on Motherboards

This subsection provides a list of routing suggestions and a list of component placement suggestions.

The following list contains routing recommendations:

- Minimize the length of high-frequency signals.

- Route differential signal pairs together.

- Minimize the use of vias for high-frequency signals.

The following list contains component placement recommendations.

- Refer to the *PCI Local Bus Specification, Revision 2.1* for the placement of the 21145 with relation to the PCI bus.

- Place the 21145 as close to the PHY device as possible.

- Place the PHY device as close to the filters and magnetics as possible.

- Place the filters and magnetics as close to the RJ45 connector as possible.

### **1.6.2** Suggestions for FCC Compliance

Product designs and their associated applications are unique. Therefore, the designer must consider the total system or module implementation when determining a product design for FCC compliance.

The following information is provided as suggestions only to aid the designer in meeting FCC regulations.

### **1.6.2.1** Suggestions for Quiet Ground and Power Planes

For quiet ground and power planes, consider the following suggestions:

- Isolate power plane for PLL stability and noise isolation of audio digital-analog converters and amplifiers.

- Partition ground planes to isolate the I/O from common system noise. Do not route any etch across an isolated or partitioned ground plane.

- *Note:* Ground plane splits can affect a signal's return path back to its source. If the signal return path is along the ground plane underneath the signal etch, any interruption in the ground plane increases the return path loop area, which in turn, increases its ability to radiate.

- Add common-mode chokes to the design at the output of the isolation transformer to isolate the I/O from common system noise.

- Place high-speed signals between power and ground planes to reduce board-level radiation.

The following books are recommended as additional references:

- Fundamentals of Electromagnetic Capability, by William G. Duff

- Engineering Electromagnetic Capability, by V. Prasad Kodali

#### **1.6.2.2** Suggestions for Routing

For routing information, consider the following suggestions:

- Never route any etch (power or ground) across a partition or void because the signal loses its return-path integrity and contaminates the isolated plane.

- Avoid placing oscillators, phase-locked loops, and other clock-type devices near I/O connectors.

- Route all critical signals (for example; clocks, video output) directly in the etch and avoid, if possible, using vias (signal paths routed between planes in an etch board).

- *Note:* Critical signals should be prioritized from the fastest to the slowest with respect to frequency and rise time. The fastest critical signals should be routed first.

# 2.0 QS6611 SYM PHY Network Implementation

This section describes how to interface the 21145 with the Quality Semiconductor QS6611 10/100BASE-TX transceiver (referred to as the QS6611).

# 2.1 QS6611 Overview

The QS6611 is a low-power CMOS 10/100BASE-TX transceiver that connects 'gluelessly' to the 21145. These two devices implement a complete 10/100 Fast Ethernet system with Auto-Negotiation, and a combined power dissipation under 1 W. The QS6611 provides a highly integrated, low-power replacement for previous BiCMOS solutions. It is suitable for use in adapters, routers, switches, both half- and full-duplex, and repeaters/hubs including 'Class II' types. The QS6611 performs transceiver, filter, and clock functions that minimize external components and their associated noise pickup and emissions. It also includes a switchable network interface port for both 10BASE-T and 100BASE-TX operation through common magnetics, eliminating the need for dual magnetics and/or external switches or jumpers.

Information on Quality Semiconductor products is available at the following website:

http://www.qualitysemi.com

#### 2.1.1 Features

The QS661 has the following features:

- Low-power all-CMOS design; 1/3-power of BiCMOS: less than 80 mA

- MLT-3 transceiver with PLL clock generation and recovery

- Category 5 UTP and Type 1 STP support

- Replacement for AM78965/6, NS83223, 10BASE-T transmit and receive filters, and 10/100 switching to magnetics

- Integrated waveshaping

- 5-bit symbol interface to PCS

- Built-in PLL loop filters to minimize external components and noise coupling

- Adaptive equalization for phase and amplitude compensation

- BASE-line wander compensation

- Built-in test modes including local and remote loopback

- Serial interface to external 10BASE-T transceiver

- On-chip filters for both 10BASE-T and 100BASE-TX

- Switched interface to common magnetics for 10/100 Mb/s modes

- Single 5 V power supply

- 64-pin QFP and TQFP surface mount packages

### 2.1.1.1 Features and Benefits

Table 9 outlines the QS6611 features and benefits.

Table 9.QS6611 Features and Benefits

| Features                                                | Benefits                                      |

|---------------------------------------------------------|-----------------------------------------------|

| Fully CMOS                                              | Low power; less than 80 mA                    |

| Adaptive equalizer                                      | Adapts automatically to various cable lengths |

| QFP and VQFP (thin) packs                               | PCI/CardBus/hubs/switcher                     |

| 10BASE-T transmit filters                               | No external hybrid L-C filters                |

| 10/100 multiplexing                                     | No external relay or switchers                |

| Crystal-ready 125/20 MHz clock synthesis                | 1/3-cost of oscillator module                 |

| Digital clock recovery PLL with integrated loop filters | No external loop filter components required   |

# 2.2 QS6611 System Diagram

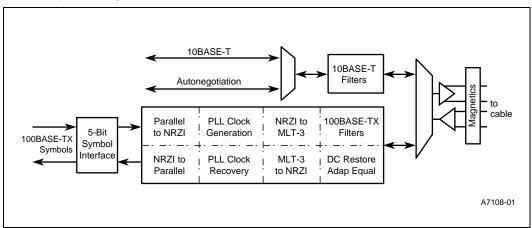

Figure 8 shows the system diagram for the QS6611.

#### Figure 8. QS6611 System Diagram

# 2.3 QS6611 Schematic

This section describes how to connect the QS6611 to the network and to the 21145, and provides layout considerations.

### 2.3.1 Network Connections

Figure 9 shows how to connect the QS6611 to the network.

Figure 9. QS6611 Connection to the RJ45-8

intel

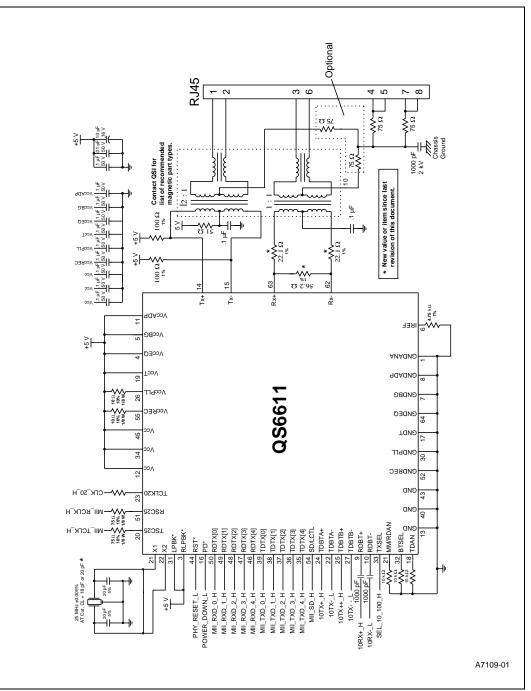

# 2.3.2 21145 Connections

Figure 10 shows how to connect the QS6611 to the 21145.

# 2.3.3 Layout Considerations

Consider the following recommendations in Table 10 for the PWB layout of the QS6611 and 21145 in a PCI adapter.

Table 10.

QS6611 PWB Layout Recommendations

| Recommendation                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Comments                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Place the 4.75 k $\Omega$ , 1%, 1/8 W current reference resistor within 1.5 cm away from the IREF pin (pin 6). (See Figure 9.)                                                                                                                                                                                                                                                                                                                                 | A 4.75 k $\Omega$ resistor will ensure the transmitting amplitude to be within 2 V peak-to-peak, +/15%.                                                                                                                                                                                       |

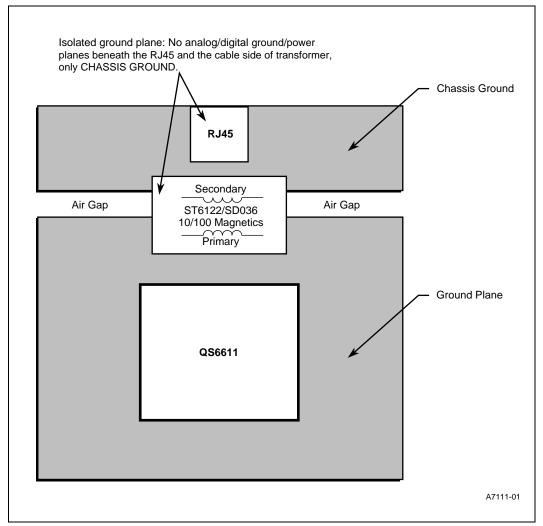

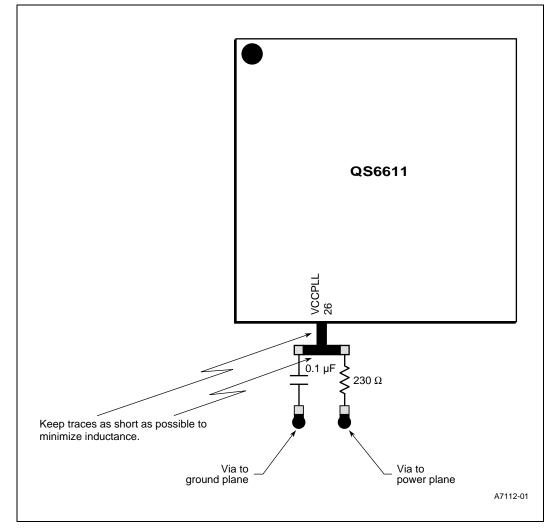

| Layout the 10 $\Omega$ resistor and the 1.0 $\mu$ F capacitor for pin 26 and for pin 55 with trace lengths less than 3 mm as shown in Figure 12.                                                                                                                                                                                                                                                                                                               | These resistor and capacitor circuits filter noise from the<br>PLL circuitry to reduce potential errors due to noisy<br>environments. The RC components need to be placed as<br>close to the pins as possible to be effective.                                                                |

| Remove 75 $\Omega$ from the center tap of the transmitting secondary side of the transformer.                                                                                                                                                                                                                                                                                                                                                                  | This is to avoid common-mode noise being injected back to the ground plane. By removing the 75 $\Omega$ resistor, EMI testing improved by typically 6 dB on several designs.                                                                                                                  |

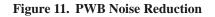

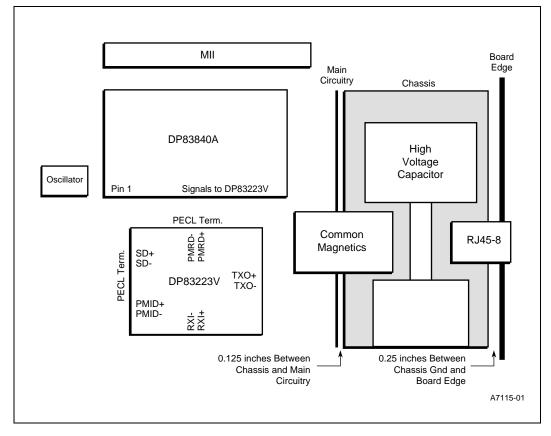

| Refer to Figure 11 for recommended parts positioning.<br>Place the QS6611, the transformer module, and the RJ45<br>connector as close to each other as possible for best<br>transmission and least noise pickup and emissions.                                                                                                                                                                                                                                 | The area under the RJ45 connector and the near edge of the magnetics module (under the pins) should be isolated from the Vcc and ground planes, and should have its own "chassis ground" plane as shown in Figure 11.                                                                         |

| Do not segment the Vcc power plane or ground plane. Use<br>a single, continuous plane for Vcc and ground to which all<br>power pins (Vcc and Gnd) will connect through vias as<br>close to the pins as possible.                                                                                                                                                                                                                                               | Splitting the Vcc power supply plane into segments for different Vcc pins on the QS6611 is not needed, and may cause problems in bypassing the various segments.                                                                                                                              |

| Refer to Figure 9 for recommended pin connections.                                                                                                                                                                                                                                                                                                                                                                                                             | Certain unused pins on the QS6611 need to be tied high or low as shown in Figure 9.                                                                                                                                                                                                           |

| For best results, use a crystal, rather than a clock oscillator.<br>Place the crystal as close to the X1 and X2 pins (pins 21<br>and 22) as possible, and keep traces short and direct.                                                                                                                                                                                                                                                                        | Use 25 MHz ±0.005%, CL = 39 pF, AT Cut, Parallel<br>Resonant (for example, ECS250.18).                                                                                                                                                                                                        |

| Place the 4.99 k $\Omega$ , 1%, 1/8 W current reference resistor as close to the IREF pin (pin 6) as possible.                                                                                                                                                                                                                                                                                                                                                 | See Figure 11.                                                                                                                                                                                                                                                                                |

| Keep transmit and receive pair runs as short as possible.<br>Keep the separation between the two conductors of each<br>pair fairly wide, 1 or 1.5 mm if possible, using the same<br>separation width all along the run to improve transmission<br>characteristics. Keep the separation between adjacent pairs<br>on the same layer (or adjacent layers not separated by a<br>power or ground plane) wide, 2 mm or more if possible, to<br>minimize cross-talk. | Transmit and receive pairs should not cross over each other.<br>They should not be laid one on top of the other on adjacent<br>planes (but this is allowed if a power or ground plane is<br>placed between the other planes). The two traces of a pair<br>should never cross over each other. |

| Keep high-frequency traces short, and space them apart from<br>each other and from traces that may be sensitive, to improve<br>transmission and reduce cross-talk. Especially sensitive are<br>clock lines, high-speed bus lines, high-impedance lines<br>(passively-driven lines), analog lines, and the symbol interface<br>lines.                                                                                                                           | Where long, high-speed lines cannot be avoided, ringing<br>and echo problems can be treated with series resistors at the<br>source end and termination resistors to ground or Vcc at the<br>far ends.                                                                                         |

| Never route clock or high-speed signal lines immediately<br>under the body of the QS6611 chip.                                                                                                                                                                                                                                                                                                                                                                 | If there is a ground or power plane shielding the QS6611, it is allowed.                                                                                                                                                                                                                      |

| Layout pads for the 230 $\Omega$ resistor and 0.1 $\mu$ F capacitor on pin 26, and minimum length traces as shown in Figure 12.                                                                                                                                                                                                                                                                                                                                | Later revision of the QS6611 will probably not need this resistor. The recommended layout allows omission of this resistor without PCB layout change.                                                                                                                                         |

| Use two 1000 pF capacitors in the RDBT± line (pins 9 and 10) to decouple the DC common-mode voltage between the 21145 and the QS6611.                                                                                                                                                                                                                                                                                                                          | See Figure 9.                                                                                                                                                                                                                                                                                 |

### 2.3.4 Ground-Plane Partitioning

As shown in Figure 11, isolating circuits on the primary side from the secondary side of the transformer with an air gap can reduce noise.

# 2.3.5 VCCPLL Connections

Figure 12 shows how to connect the VCCPLL pin on the QS6611.

# **3.0 DP83840A MII PHY Network Implementation**

This section contains the design recommendations for the National Semiconductor DP83840A 10/100 Mb/s PHY device and the DP83223V TWISTER High-Speed Networking Transceiver (referred to as the DP83840A and DP83223V) in a node application using the 21145.

# 3.1 DP83840A and DP83223V Overview

The DP83840A PHY device incorporates an integrated 10BASE-T transceiver as well as an MII for a connection to the 21145. The DP83840A is fully compatible with the DP83223V to enable 100BASE-TX compliant signaling.

A design based on these three devices allows for a simple low-cost PCI node design, which will support both 10BASE-T and 100BASE-TX protocols. The comprehensive feature sets of both the 21145 and the DP83840A support several different modes of functionality.

Although design issues such as common magnetics, autonegotiation, and 10/100 Mb/s operation are noted here, detailed emphasis is placed on fundamental design requirements from the MAC layer to the RJ45-8 connector. Schematic diagrams, layout considerations, and power requirements are all provided in this application note. A magnetics scheme is recommended to help the designer integrate the National Semiconductor parts in a system.

For a given application, the component values and design suggestions in this section can and will vary with the particular design. This section illustrates the function of the various components and their relationship to overall system performance. With this knowledge, the system designer can make modifications to the recommendations with an understanding of the potential impact to the system.

Information on National Semiconductor products is available at the following website:

http://www.national.com

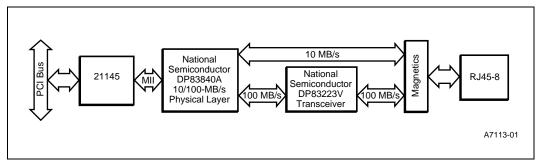

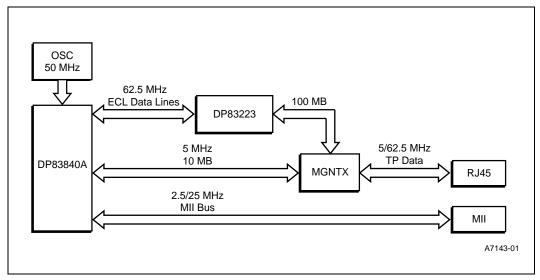

# 3.2 DP83840A and DP83223V Block Diagram

Figure 13 is the system diagram for a node application. The following sections describe the blocks. For more detailed information on the specifications of these parts, see the documentation listed in Appendix B.

Figure 13. 10/100 Mb/s Block Diagram

# **3.3 DP83840A Description**

The DP83840A finds wide application in data communication systems. It is a PHY device for Ethernet 10BASE-T and 100BASE-X using Category 5 (CAT5) unshielded, Type 1 shielded, and fiber-optic cables. It interfaces to the PMD sublayer through a DP83223V and to the MAC layer through the MII, ensuring interoperability between products from different vendors.

The DP83840A system architecture is based on the integration of the following National Semiconductor industry-proven core technologies:

- 10BASE-T ENDEC/Transceiver module to provide the 10 Mb/s IEEE 802.3 functions

- 100BASE-X physical coding sublayer (PCS) and control logic that integrate the core modules into a dual-speed Ethernet physical layer controller

The DP83840A features include:

- IEEE 802.3 10BASE-T compatibility. ENDEC and UTP/STP transceivers and filters are built in.

- IEEE 802.3 100BASE-X compatibility with support for Category 5 UTP, Type 1 STP, and fiber-optic transceivers. Connects directly to the DP83223V.

- ANSI X3T12 TP-PMD compatibility.

- IEEE 802.3 autonegotiation for automatic speed selection.

- Independent interface (MII) with serial management interface.

- Integrated, high-performance, 100 Mb/s clock recovery circuitry that requires no external filters.

- Full-duplex support for 10 Mb/s and 100 Mb/s.

- MII serial 10 Mb/s output mode.

- Programmable loopback modes for easy system diagnostics.

- Flexible LED support.

# **3.4 DP83223V Description**

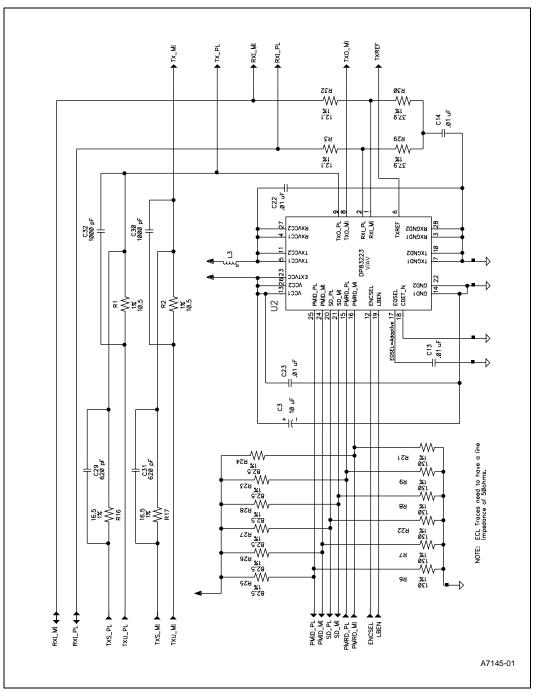

The DP83223V twisted-pair transceiver can drive and receive either binary or MLT-3 encoded data streams. The DP83223V allows links of up to 100 m (328 ft.) over both STP and data grade UTP or equivalent. The DP83223V also provides important features such as tristate-capable transmit outputs, and controlled transmit output edge rates (to reduce EMI radiation) for both binary and MLT-3 modes of operation.

The DP83223V features include:

- Integrated transmitter and receiver with adaptive equalization circuit.

- Programmable binary or MLT-3 operation.

- Isolated TX and RX power supplies for minimum noise coupling.

- Controlled transmit output edge rates for reduced EMI.

- Tristate-capable current transmit outputs.

- Loopback feature for board diagnostics.

- Programmable transmit voltage amplitude.

### 3.4.1 Magnetics

The magnetics block in Figure 13 uses a common magnetics scheme that allows 10 Mb/s and 100 Mb/s data to coexist in the same magnetics package. The concept of common magnetics is based on the interoperation of the DP83840A and the DP83223V, and allows for either 10 Mb/s or 100 Mb/s operation with the use of a single magnetics module and RJ45-8 media connector. (For a complete discussion of the common magnetics concept, refer to the National Semiconductor *10/100 Ethernet Common Magnetics* application note.)

National Semiconductor has patents on a common magnetics scheme, and provides a license to purchasers of both the DP83840A and the DP83223V components to use the common magnetics scheme in their design. Several suppliers have indicated that they intend to provide magnetic components for the National Semiconductor recommended implementation. Appendix A contains a list of these magnetics vendors and the license agreement. This is not an exhaustive list and other vendors could be considered, but the transformer would need to be characterized in relation to the *10/100 Base-T Magnetics Specification* (available from National Semiconductor).

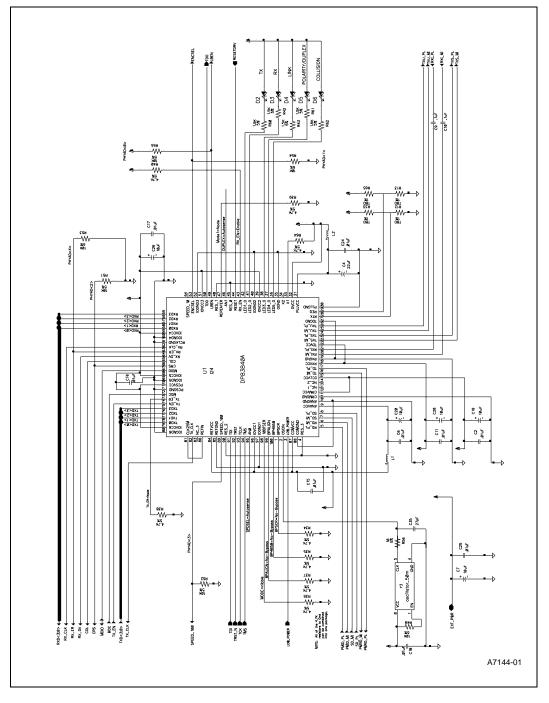

### 3.4.2 DP83840A and DP83223V Schematic Diagram

Appendix A contains the schematic diagrams for the PHY. Figure 44 illustrates the interconnection of the DP83840A and DP83223V.

#### 3.4.3 Media-Independent Interface (MII)

The DP83840A has a standard IEEE 802.3 MII for connection to external 10 Mb/s or 100 Mb/s PHYs. This comprises nibblewide (4-bits) transmit and receive data streams, transmit and receive clocks, transmit enable, receive collision, receive carrier sense, receive data valid, data error, and serial management data clock and data signals. These signals are: TX\_CLK, TXD[3:0], TX\_EN, CRS, COL, RXD[3:0], RX\_CLK, RX\_DV, RX\_ER, MDC, and MDIO.

The MII supports two nibble clock rates:

- 2.5 MHz for 10 Mb/s operation

- 25 MHz for 100 Mb/s operation

Operation at 10 Mb/s or 100 Mb/s is transparent to the host.

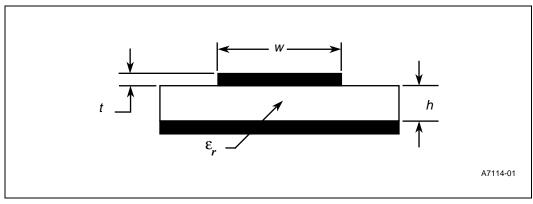

#### **3.4.4** Signal Terminations

The trace impedance of each MII line should be approximately 68  $\Omega$  per the IEEE specification. The design of microstrips for PC boards is straightforward and a function of the microstrip width (*w*), thickness (*t*), height (*h*), and the relative electric permittivity of the substrate ( $\varepsilon$ ), as shown in Figure 14.

#### Figure 14. Microstrip impedance

Equation 1 shows how the various geometric and material parameters on the printed circuit board (PCB) control the impedance of the trace. Most of the PCB programs calculate the trace impedance directly.

**Equation 1. Microstrip Impedance**

$$Z = \left(\frac{87}{(\sqrt{\varepsilon_r + 1.41})}\right) \ln\left(\frac{5.98h}{(0.8w+t)}\right)$$

The DP83840A supports 10 Mb/s and 100 Mb/s Ethernet using the DP83223V and the common magnetics approach. The following signal lines between the DP83840A and the DP83223V should be PECL (Thevenin) terminated at the DP83223V: PMRD+, PMRD-, PMID+, PMID-, SD+, and SD-. These signal lines are Thevenin terminated (see Figure 48) with an equivalent resistance equal to the trace impedance. This trace impedance should be controlled and match the device termination resistance. For the preferred case of a 50  $\Omega$  transmission interconnect, resistors R23 through R28 are 82.5  $\Omega$  to **Vcc**, and R6 through R9, R21, and R22 are 130  $\Omega$  to ground. This generates a 50.3  $\Omega$  Thevenin resistance. The trace impedance of these signal lines should also be 50  $\Omega$ .

# intel

It is critical that these lines be kept short (<1 inch) and that termination resistors are as close as possible to the destination. If the PECL termination resistors are not placed close to the signal destination, reflections might result and could corrupt the signal integrity. The midlevel voltage of the termination network should be 3 V and the required bias current is 23.5 mA due to each line termination.