August 1999

## Interfacing 16Cxxx UARTs to a CPU

Author: Reinhardt Wagner

### **Introduction**

Due to the variety of CPUs that can be used in conjunction with UARTs, an understanding of a UART's CPU interface is useful. This allows establishing the compatibility of a particular CPU bus and the design for minimal glue logic as well as optimized bus cycle timing.

UARTs are usually driven by a CPU. EXAR's 16Cxxx UART family (16C45x, 16C55x, 16C65x and 16C85x 16C145x, 16C155x, 16C245x, 16C255x series) directly supports the INTEL bus interface. INTEL-derived CPUs are commonly interfaced to these UARTs despite data-, address- and control-bus timing variations from CPU type to CPU type.

It is possible to control UARTs by programmable logic, like FPGAs, instead of a CPU or microcontroller. This also affords a clear understanding of the interface logic.

#### Control Logic

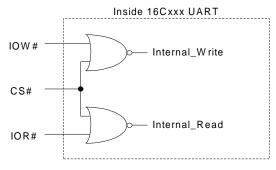

Internal to the 16Cxxx UARTs, the CPU-bus control signals IOR#, IOW# and CS# are logically associated as shown in Figure 1.

#### Figure 1

Hence the sequence of applying IOR# and CS# during a Read Cycle and IOW# and CS# during a Write Cycle is unimportant. The following discussion thus refers to the internal UART signals (IOR# +CS#) and (IOW# + CS#) instead of IOR#, IOW# and CS#.

# DATA COMMUNICATIONS APPLICATION NOTE CANNON CANNON

#### Read Cycle

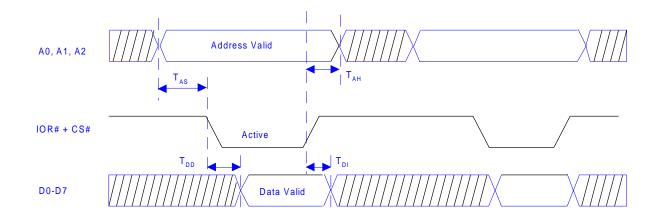

In order for the CPU to perform a Read of the UART's registers, the bus signal sequence should conform to the timing shown in Figure 2.

Figure 2: Read Cycle

The address stable time has to span the (IOR# + CS#) active period – even if the data is read early in this period. The reason being that the address bus is not latched edge triggered, but is level sensitive. Hence, changing the address during the IOR/CS active period may cause a read of another register – whose contents could subsequently change.

An example of this is the case for an unintended read of the ISR register when an interrupt is pending. This would clear the interrupt.

Visit Exar Web Site at www.exar.com

**EXAR** Corporation, 48720 Kato Road, Fremont, CA 94538 · (510) 668-7000 · FAX (510) 668-7017

### Write Cycle

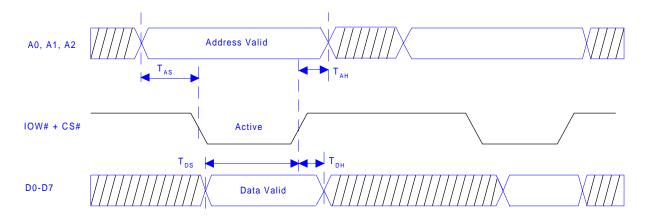

The Write Timing of the 16Cxxx UARTs should comply with the timing shown in Figure. 3.

### Figure 3: Write Cycle

The UART latches the data on the (IOW# + CS#) rising edge. The address bus needs to be stable during the whole (IOW# + CS#) active period.

#### **Timing Parameters**

The values of the Timing Parameters shown in the above Figures are specified in the Electrical Characteristics Table, Figure 4. These are common to all of EXAR's 16Cxxx family of UARTs and are representative of the design and technology of UARTs manufactured since early 1997.

| Symbol          | Parameter          | Limits 3.3V |     | Limits 5V |     | Units | Conditions |

|-----------------|--------------------|-------------|-----|-----------|-----|-------|------------|

|                 |                    | Min         | Max | Min       | Max |       |            |

| T <sub>AS</sub> | Address Setup Time | 10          |     | 5         |     | ns    |            |

| T <sub>AH</sub> | Address Hold Time  | 10          |     | 5         |     | ns    |            |

| T <sub>DY</sub> | Data Delay Time    |             | 50  |           | 35  | ns    | 100pF load |

| T <sub>DI</sub> | Data Disable Time  |             | 35  |           | 25  | ns    | 100pF load |

| T <sub>DS</sub> | Data Setup Time    | 10          |     | 5         |     | ns    |            |

| T <sub>DH</sub> | Data Hold Time     | 10          |     | 5         |     | ns    |            |

Figure 4: Timing Parameter Specifications

The Data Delay Time,  $T_{DY}$ , and the Data Disable Time,  $T_{DI}$ , depend on the data bus loading that the UARTs sees during the write cycle. Hence a lighter load will result in faster times.

3

Visit Exar Web Site at www.exar.com

EXAR Corporation, 48720 Kato Road, Fremont, CA 94538 · (510) 668-7000 · FAX (510) 668-7017

#### NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to im-prove design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits de-scribed herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publicatio has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circum-stances.

Copyright 1999 EXAR Corporation.

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.

Visit Exar Web Site at www.exar.com

EXAR Corporation, 48720 Kato Road, Fremont, CA 94538 · (510) 668-7000 · FAX (510) 668-7017

4